Delft University of Technology Faculty of Electrical Engineering, Mathematics and Computer Science Circuits & Systems Group

# Scheduling Toolbox for MATLAB

**Reference Guide**

Version 0.9

Ing. H.J. Lincklaen Arriëns January 2006

Scheduling Toolbox for MATLAB *Reference Guide* © H.J. Lincklaen Arriëns 2006

The author assumes no responsibility whatsoever for use of the software by other parties, and makes no guarantees, expressed or implied, about its quality, reliability, or any other characteristic. Acknowledgement if the software is used is appreciated.

MATLAB is a registered trademark of The MathWorks, Inc.

Graphviz - Graph Visualization Software has originally been developed by AT&T Research, and is licensed on an open source basis under The Common Public License. See <u>http://www.graphviz.org/</u>

#### **Table of Contents**

| Categorical Listing of Functions      |

|---------------------------------------|

| Alphabetical Listing of Functions     |

| ALAP5                                 |

| ALU6                                  |

| ASAP7                                 |

| cirInfo8                              |

| fixp2hex9                             |

| forceD                                |

| gen_INP11                             |

| gen_mTB12                             |

| hex2fixp16                            |

| listSched17                           |

| MUL                                   |

| parse                                 |

| read_OUT                              |

| showDistrib21                         |

| showGraph22                           |

| toAdjMat23                            |

| toSFixp24                             |

| toUFixp                               |

| view_cir_IO26                         |

| xplore                                |

| schedGUI                              |

| Structure and syntax of the .cir file |

| Signed fixed-point notation           |

| Setup of the .INP- and .OUT-files     |

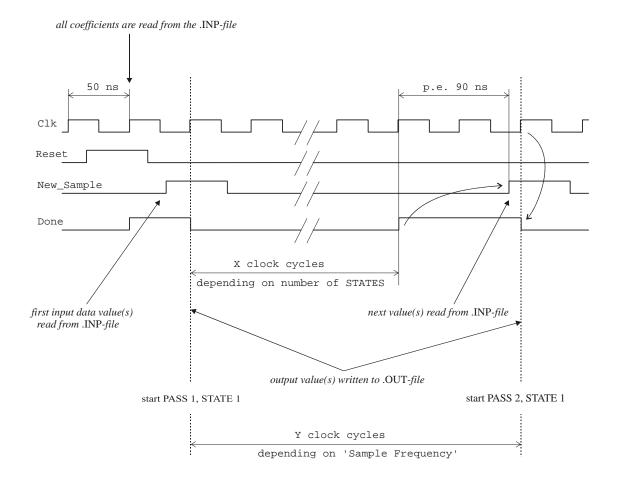

| Simulation timing setup               |

| Overview of the Software Environment  |

| VHDL resources                        |

#### **Categorical Listing of Functions**

| MATLAB resource descriptions simulating their VHDL behavior |                                                                    |  |

|-------------------------------------------------------------|--------------------------------------------------------------------|--|

| ALU                                                         | Simulate the behavior of the VHDL description of a registered ALU. |  |

| MUL                                                         | Simulate the behavior of the VHDL description of a MULtiplier.     |  |

| Scheduling functions |                                                          |

|----------------------|----------------------------------------------------------|

| ALAP                 | Find the SSG using the ALAP method.                      |

| ASAP                 | Find the SSG using the ASAP method.                      |

| forceD               | Find the SSG using the Force Directed Scheduling method. |

| listSched            | Find the SSG using a List Scheduling method.             |

| Fixed-point translation and manipulation functions |                                                                            |  |

|----------------------------------------------------|----------------------------------------------------------------------------|--|

| fi xp2hex                                          | Convert a signed value to a hex string represented by fxd-bits.            |  |

| hex2fi xp                                          | Convert a hex string given by fxd-bits into its signed decimal equivalent. |  |

| toSFi xp                                           | Converts a signed fractional value to fit in SFxd bits.                    |  |

| toUFi xp                                           | Converts a signed fractional value to fit in UFxd bits.                    |  |

| Info, Graph and sch | nedule viewers                                                       |  |

|---------------------|----------------------------------------------------------------------|--|

| ci rl nfo           | Extract and display some information from a .cir-file.               |  |

| read_OUT            | Convert the hex data in an .OUT-file into decimal format.            |  |

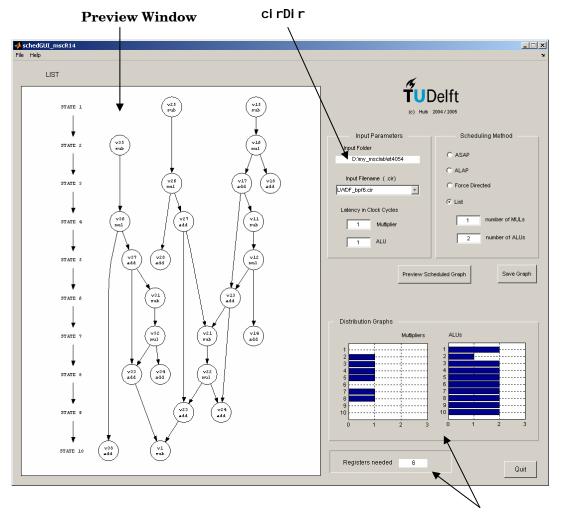

| schedGUI            | M-file for schedGUI.fig                                              |  |

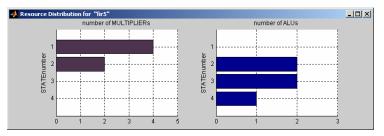

| showDistrib         | Plot resource usage versus clock STATEs.                             |  |

| showGraph           | Converts 'graph.dot' to an image and opens a viewer to show it.      |  |

| view_cir_10         | Graphical view of input circuit description.                         |  |

| xpl ore             | Plot design evaluation space information for a cir-file description. |  |

| Testbench and MATLAB / VHDL file generators |                                                      |  |

|---------------------------------------------|------------------------------------------------------|--|

| gen_mTB                                     | Create MATLAB reference testbench files.             |  |

| gen_VHD                                     | Create testbench, wrapper and SSG-module VHDL-files. |  |

| Utilities, mostly for | internal use only                                                |

|-----------------------|------------------------------------------------------------------|

| axDrag2               | Pan and zoom with mouse and simple keystrokes.                   |

| groupl Os             | For internal use only.                                           |

| hpgPI ot              | Plot a .hpg-file in schedGUI's preview window.                   |

| lifeTimes             | For internal use only (registered outputs in resources assumed). |

| mapResources          | For internal use only (registered outputs in resources assumed). |

| parse                 | Read and convert a .cir-file into internal data format.          |

| schedul e             | Determines a time schedule (SSG).                                |

| showREGs              | Plot REGister usage.                                             |

| startup               | Setup paths for msclab_et4054.                                   |

| toAdj Mat             | Converts an interconnection table into an adjacency matrix.      |

| Graphical User Interface | 9                                                        |

|--------------------------|----------------------------------------------------------|

| schedGUI                 | GUI that combines most of the above mentioned functions. |

#### Alphabetical Listing of Functions

#### for general use

| ALAP        | Find the SSG using the ALAP method.                                        |  |  |

|-------------|----------------------------------------------------------------------------|--|--|

| ALU         | Simulate the behavior of the VHDL description of a registered ALU.         |  |  |

| ASAP        | Find the SSG using the ASAP method.                                        |  |  |

| cirlnfo     | Extract and display some information from a .cir-file.                     |  |  |

| fi xp2hex   | Convert a signed value to a hex string represented by fxd-bits.            |  |  |

| forceD      | Find the SSG using the Force Directed Scheduling method.                   |  |  |

| gen_I NP    | Write data into the correct format for an .INP-file.                       |  |  |

| gen_mTB     | Create MATLAB reference testbench files.                                   |  |  |

| gen_VHD     | Create testbench, wrapper and SSG-module VHDL-files.                       |  |  |

| hex2fi xp   | Convert a hex string given by fxd-bits into its signed decimal equivalent. |  |  |

| listSched   | Find the SSG using a List Scheduling method.                               |  |  |

| MUL         | Simulate the behavior of the VHDL description of a MULtiplier.             |  |  |

| parse       | Read and convert a .cir-file into internal data format.                    |  |  |

| read_OUT    | Convert the hex data in an .OUT-file into decimal format.                  |  |  |

| schedGUI    | M-file for schedGUI.fig                                                    |  |  |

| showDistrib | Plot resource usage versus clock STATEs.                                   |  |  |

| showGraph   | Converts 'graph.dot' to an image and opens a viewer to show it.            |  |  |

| toAdj Mat   | Converts an interconnection table into an adjacency matrix.                |  |  |

| toSFi xp    | Converts a signed fractional value to fit in SFxd bits.                    |  |  |

| toUFi xp    | Converts a signed fractional value to fit in UFxd bits.                    |  |  |

| view_cir_I0 | Graphical view of input circuit description.                               |  |  |

| xpl ore     | Plot design evaluation space information for a cir-file description.       |  |  |

#### for internal use only

| axDrag2      | Pan and zoom with mouse and simple keystrokes.                   |

|--------------|------------------------------------------------------------------|

| groupl Os    | For internal use only.                                           |

| hpgPl ot     | Plot a .hpg-file in schedGUI's preview window.                   |

| lifeTimes    | For internal use only (registered outputs in resources assumed). |

| mapResources | For internal use only (registered outputs in resources assumed). |

| schedul e    | Determines a time schedule (SSG).                                |

| showREGs     | Plot REGister usage.                                             |

| startup      | Setup paths for msclab_et4054.                                   |

#### ALAP

| Purpose     | Find the SSG using the ALAP method.                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                             |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax      | tFrames = AL                                                                                                                                                                                                                                                                                                                                                                                                              | AP(adj Mat, del ayVec)                                                                                                                                                                                                                                                      |  |

| Description | tFrames = ALAP(adj Mat, del ayVec) returns a two-column vector tFrames<br>describing the SSG (Scheduled Sequencing Graph) of the operations when<br>scheduled according to the ALAP (As Late As Possible) method (no resource<br>constraints).<br>The unscheduled flow has to be given in adj Mat with the clock delays per<br>resource type (e.g. MUL, ALU) as integer number of clock cycles specified in<br>del ayVec. |                                                                                                                                                                                                                                                                             |  |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                             |  |

| See Also    | ASAP<br>forceD<br>listSched<br>parse<br>toAdjMat                                                                                                                                                                                                                                                                                                                                                                          | Find the SSG using the ASAP method.<br>Find the SSG using the Force Directed Scheduling method.<br>Find the SSG using the List Schedu;ing method.<br>Read and convert a .cir-file into internal data format.<br>Converts an interconnection table into an adjacency matrix. |  |

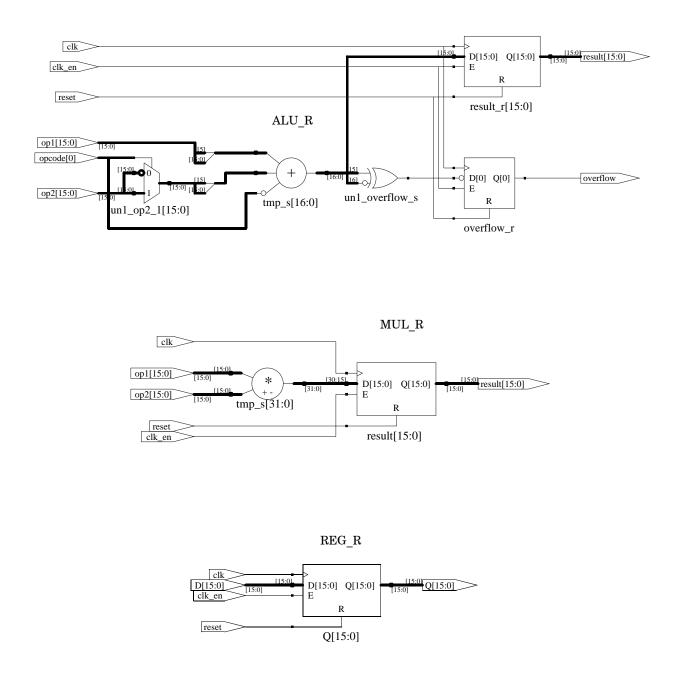

## ALU

| Purpose     | Simulate the behavior of the VHDL description of a registered ALU.                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | result = ALU(op1,op2,fxd, opcode)                                                                                                                                                                                                                                                                                                                                                                                                     |

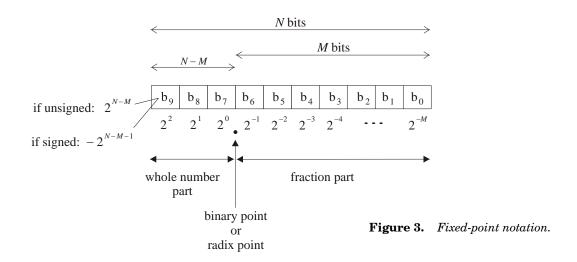

| Description | result = ALU(op1, op2, fxd, opcode) returns the result of the operation as<br>specified in opcode. Here op1 and op2 are two signed fixed-point input<br>variables, while result is the output in the same signed fixed-point format. This<br>format has to be given in the vector fxd as [N M], where N denotes the total<br>number of bits, while M defines the number of fractional bits.<br>Valid opcodes are 'add' and 'sub'.     |

|             | [result, overflow] = ALU(op1, op2, fxd, opcode, ovMode) also signals the correctness of the result in 'overflow'. A zero means that the result is unaltered and correct, overflow = 1 means that the result has been 'wrapped' (e.g. bits left of msb has been skipped) if ovMode = 'wrap' (the default choice), or has been saturated to its highest positive value or lowest negative value when ovMode = 'sat' has been specified. |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| See Also    | MUL simulate the behavior of the VHDL description of a registered multiplier.                                                                                                                                                                                                                                                                                                                                                         |

### ASAP

| Purpose     | Find the SSG using the ASAP method.                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | tFrames = AS                                                                                                                                                                                                                                                                                                                                                                                                              | AP(adjMat, del ayVec)                                                                                                                                                                                                                                                       |

| Description | tFrames = ASAP(adj Mat, del ayVec) returns a two-column vector tFrames<br>describing the SSG (Scheduled Sequencing Graph) of the operations when<br>scheduled according to the ASAP (As Soon As Possible) method (no resource<br>constraints).<br>The unscheduled flow has to be given in adj Mat with the clock delays per<br>resource type (e.g. MUL, ALU) as integer number of clock cycles specified in<br>del ayVec. |                                                                                                                                                                                                                                                                             |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                             |

| See Also    | ALAP<br>forceD<br>IistSched<br>parse<br>toAdjMat                                                                                                                                                                                                                                                                                                                                                                          | Find the SSG using the ALAP method.<br>Find the SSG using the Force Directed Scheduling method.<br>Find the SSG using the List Schedu;ing method.<br>Read and convert a .cir-file into internal data format.<br>Converts an interconnection table into an adjacency matrix. |

#### cirInfo

| Purpose     | Extract and display some information from a .cir-file.                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | cirlnfo(cirFilename)                                                                                                                                                                                                                                                                                                                                                    |

| Description | cirlnfo lists in the console window the total number of operations, and the<br>numbers of multiplications, ALU operations, coefficients, and delay elements.<br>Also the number of external inputs and outputs are listed, followed by the input<br>and output identifier names.<br>cirlnfo can be used as a first test to check a .cir-file for the absence of errors. |

| Examples    | <pre>&gt;&gt; cirInfo('FIR5.cir') totally 11 operations, of which         6 multiplications, and         5 ALU operations.     6 constant coefficients     5 delay elements     1 input(s) : i0     1 output(s): o5 &gt;&gt;</pre>                                                                                                                                      |

See Also

# fixp2hex

| Purpose<br>Syntax | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ned value to a hex string represented by fxd-bits.<br>sp2hex(decVal, fxd)                                                                                                                              |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description       | <ul> <li>hexStr = fi xp2hex(decVal, fxd) checks whether the decimal figure decVal fits in the given fxd bits and if so, returns its hexadecimal representation as a string.</li> <li>fxd is supposed to be a two-element vector [N M], where N defines the total number of available bits and M defines the number of bits to the right of the binary point.</li> <li>If M is too low to exactly represent decVal, decVal will be truncated.</li> <li>An error message is issued when N-M should be too low to represent the signed integer part of decVal.</li> <li>decVal itself can be a vector of fractional decimals.</li> </ul> |                                                                                                                                                                                                        |

| Examples          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                        |

| See Also          | hex2fi xp<br>toSFi xp<br>toUFi xp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Convert a hex string given by fxd-bits into its signed decimal<br>equivalent.<br>Converts a signed fractional value to fit in SFxd bits.<br>Converts an unsigned fractional value to fit in UFxd bits. |

#### forceD

| Purpose     | Find the SSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | using the Force Directed Scheduling method.                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | tFrames = fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | orceD(adjMat,mulOps)                                                                                                                                                                                                                                   |

| Description | <pre>tFrames = forceD(adj Mat, mul Ops) returns a two-column vector tFrames describing the SSG (Scheduled Sequencing Graph) of the operations when scheduled according to the Force Directed Scheduling method with optimal resource distribution. NOTE: At the moment, the latency of the resources (MUL, ALU) is expected         to be one clock cycle. The unscheduled flow has to be given in adj Mat, while in the vector mul Ops the resource type of the operations should be specified ( a 1 means a multiplication).</pre> |                                                                                                                                                                                                                                                        |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                        |

| See Also    | ALAP<br>ASAP<br>IistSched<br>parse<br>toAdjMat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Find the SSG using the ALAP method.<br>Find the SSG using the ASAP method.<br>Find the SSG using the List Schedu;ing method.<br>Read and convert a .cir-file into internal data format.<br>Converts an interconnection table into an adjacency matrix. |

| Reference   | Pierre G. Pau                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d Scheduling for the Behavioral Synthesis of ASIC's,<br>lin and John P. Knight,<br>m Computer-Aided Design, Vol. 8, No. 6, JUNE 1989, pages 661-679                                                                                                    |

# gen\_INP

|                  | I                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose          | Write data into the correct format for an .INP-file.                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax           | gen_INP(inpFilename, fxd, coeffs, inpSig)                                                                                                                                                                                                                                                                                                                                                                                    |

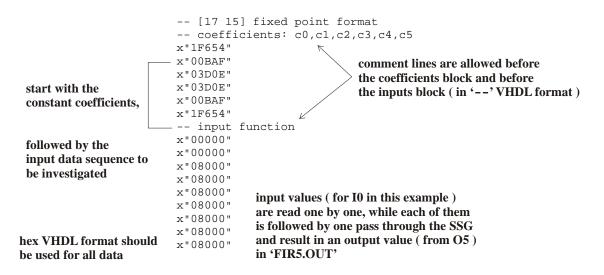

| Description      | gen_INP(i npFilename, fxd, coeffs, i npSig) creates the file i npFilename and<br>writes sequentially first all coefficients line by line, and next i npSig line by<br>line in a VHDL hex representation of the fxd format to this file. The format and<br>the start of the coefficients and the input sections will be marked with comment<br>lines. All data values are 'rounded' before they are converted to fixed-point. |

| Examples         | <pre>&gt;&gt; load coeffs_FIR5.mat<br/>&gt;&gt; coeffs<br/>coeffs =</pre>                                                                                                                                                                                                                                                                                                                                                    |

| .INP-file format | See Chapter "INP and OUT-files".                                                                                                                                                                                                                                                                                                                                                                                             |

| See Also         | read_OUT Convert the hex data in an .OUT-file into decimal format.                                                                                                                                                                                                                                                                                                                                                           |

## gen\_mTB

| Purpose     | Create MATLAB reference testbench files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | gen_mTB(cirFilename, toScreen, schedMethod, varargin)<br>coeffsSeq = GEN_MTB(cirFilename, toScreen, schedMethod, varargin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

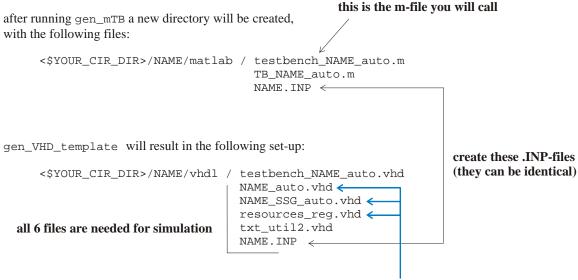

| Description | <ul> <li>gen_mTB(cirFilename, toScreen, schedMethod, varargin) creates two<br/>MATLAB files:</li> <li>a description of the SSG given in cirFilename, and a testbench-file which calls<br/>this SSG.</li> <li>If toScreen is 1, these are written to the screen; if 0, they are written to disk.<br/>If toScreen is 1, these are written to the screen; if 0, they are written to disk.<br/>If toFilename should be NAME. cir, they can be found in (a newly created<br/>directory) NAME\mat1ab.</li> <li>The (top-level) testbench-file will be named testbench_NAME_auto. m (see its<br/>HELP function), the SSG-file TB_NAME_auto. m. Input data for the testbench<br/>is expected to be found (line by line) in a (user created) file named NAME.INP,<br/>and output will be written to a file NAME.OUT, both in the directory<br/>NAME\mat1ab.</li> <li>schedMethod specifies the scheduling method to be used, and can be 'ASAP',<br/>'ALAP', 'forceD' or 'LIST'.</li> <li>The parameters that follow schedMethod (indicated with varargin here) are<br/>dependant on the method chosen, and may be values for del ayMUL, del ayALU,<br/>nMULs and/or nALUs:</li> <li>del ayMUL and del ayALU are the latencies of resp. MULtipliers and ALUs in<br/>integer multiples of a clock cycle. They are optional for 'ASAP' and 'ALAP'<br/>(default, if not specified, is 1 cycle each). At this moment they are not needed<br/>for 'forceD' (both fixed to 1). For the 'LIST' method, each of the delays<br/>needs to be specified.</li> <li>mMULs and nALUs are the number of available MULtipliers and ALUs, and<br/>have to be specified for the 'LIST' method only.</li> </ul> |

| Examples    | <pre>NOTE 1: gen_mTB expects to be run from the directory in which the .cir-file resides. NOTE 2: The fixed-point format of the .INP-file should always match the format that is passed to the testbench.  gen_mTB( 'my_file.cir', 1, 'asap' ) gen_mTB( 'my_file.cir', 0, 'alap', 2, 1 ) gen_mTB( 'my_file.cir', 0, 'forceD' ) coeffsSeq = gen_mTB( 'my_file.cir', 0, 'list', 1, 1, 3, 2 )  &gt;&gt; help testbench_my_file_auto Syntax: TESTBENCH_ my_file_AUTO(SFxd3,DBG)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

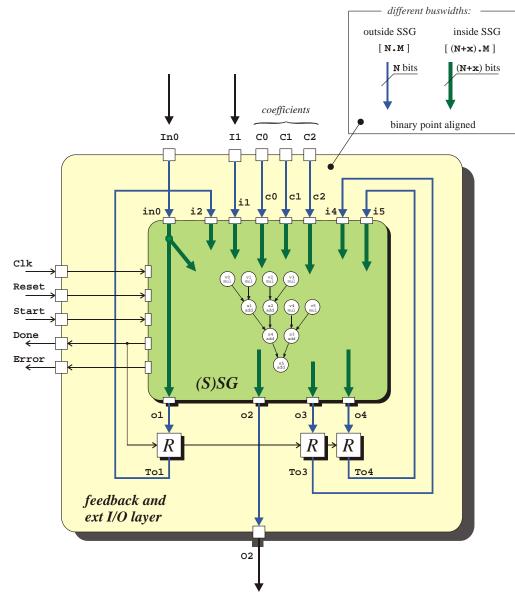

SFxd3 defines width of signed fractional fixed-point databus in vector [N M x], where N is the total number of bits of the external I/O bus from which M are fractional bits. x defines an additional number of bits with which N should be extended inside the SSG. If DBG = 1, intermediate results are printed. Needs 'MY\_FILE.INP' in current directory to read input data from, writes 'MY\_FILE.OUT' with results.

.INP-file format See Chapter "INP and OUT-files".

See Also gen\_VHD Create testbench, wrapper and SSG VHDL-files.

## gen\_VHD

| Purpose     | Create testbench, wrapper and SSG-module VHDL-files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | gen_VHD (cirFilename, SFxd3, toScreen, schedMethod, varargin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description | <pre>gen_VHD(ci rFilename, SFxd3, toScreen, schedMethod, varargin) creates the<br/>VHDL files needed for simulation and synthesis ( a testbench, a wrapper and the<br/>SSG-module VHDL-files).</pre> SFxd3 should be a 3-element vector [N M x], in which N indicates the external<br>buswidth (signed fixed-point), M the number of bits of N to be used for the<br>fraction part, and x an additional number of bits for extending (the whole-<br>number part of) N inside the SSG (to allow for intermediate results greater or<br>less than can be represented with N bits).<br>If toScreen is 1, the files are written to the screen; if 0, they are written to disk.<br>If ci rFilename should be NAME.cir, they can be found in (a newly created<br>directory) NAME\vhd1.<br>The (top-level) testbench-file will be named testbench_NAME_auto.vhd, the<br>wrapper file NAME_auto.vhd, and the SSG-file NAME_SSG_auto.vhd.<br>For simulation all vhd-files placed in the directory are needed, e.g. also the files<br>resources_regd.vhd and txt_util2.vhd.Input data for the testbench is<br>expected to be found (line by line) in a (user created) file named NAME.INP, and<br>output will be written to a file NAME.OUT<br>Synthesis needs the files resources_reg.vhd, NAME_SSG_auto.vhd and as top<br>level file NAME_auto.vhd. |

|             | <ul> <li>dependant on the method chosen, and may be values for del ayMUL, del ayALU, nMULs and/or nALUS:</li> <li>del ayMUL and del ayALU are the latencies of resp. MULtipliers and ALUs in integer multiples of a clock cycle. They are optional for 'ASAP' and 'ALAP' (default, if not specified, is 1 cycle each). At this moment they are not needed for 'forceD' (both fixed to 1). For the 'LIST' method, each of the delays needs to be specified.</li> <li>nMULs and nALUS are the number of available MULtipliers and ALUs, and have to be specified for the 'LIST' method only.</li> <li>NOTE 1: gen_VHD expects to be run from the directory in which the .cir-file resides.</li> <li>NOTE 2: The fixed-point format of the .I NP-file should always match the format that is passed to the testbench.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Examples    | gen_VHD( 'my_file.cir', [16 15 0], 1, 'asap' )<br>gen_VHD( 'my_file.cir', [16 15 2], 0, 'alap', 2,1 )<br>gen_VHD( 'my_file.cir', [32 30 4], 0, 'forceD' )<br>gen_VHD( 'my_file.cir,' [24 20 8], 0, 'list', 1,1, 3,2 )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

```

The command

>> gen_VHD( 'FIR5.cir', [17 15 1], 0, 'asap' )

will result in an entity definition in FIR5_auto. vhd that looks like:

entity FIR5 is

generic ( N_g

: positive := 17;

M_g

: positive := 15;

NX_g

: positive := 18;

MUL_delay_g : Time := 5 ns;

ALU_delay_g : Time := 2 ns;

REG_del ay_g : Time := 2 ns );

port (CIk

: in std_logic;

in std_logic;

Reset

:

New_Sample : in std_logic;

C0 : in std_logic_vector(N_g-1 downto 0);

in std_logic_vector(N_g-1 downto 0);

C1 :

C2 :

in std_logic_vector(N_g-1 downto 0);

C3 : in std_logic_vector(N_g-1 downto 0);

C4 :

in std_logic_vector(N_g-1 downto 0);

C5 :

in std_logic_vector(N_g-1 downto 0);

10 : in std_logic_vector(N_g-1 downto 0);

05 : out std_logic_vector(N_g-1 downto 0);

Done

: out std_l ogi c;

Error

: out std_logic

);

end FIR5;

Create MATLAB reference testbench files.

See Also

gen_mTB

```

# hex2fixp

| Purpose     | Convert a hex                                                                                                                                                                                                                                                                                                                                                                                                                                                | string given by fxd-bits into its signed decimal equivalent.                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | decVal = hex                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre> 2fi xp(hexStr, fxd)</pre>                                                                                                                                                          |

| Description | <ul> <li>decVal = hex2fi xp(hexStr, fxd) converts hexStr into a (possibly fractional) signed decimal value in fxd bits.</li> <li>fxd is supposed to be a two-element vector [N M], where N defines the total number of available bits and M defines the number of bits to the right of the binary point.</li> <li>An error message is issued when decVal cannot be represented in the given fxd bits.</li> <li>hexStr can be an array of strings.</li> </ul> |                                                                                                                                                                                          |

|             | <b>NOTE:</b> usually MATLAB's ' format long' will be necessary to represent the result with enough decimals (avoid rounding to 'short' format).                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                          |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                          |

| See Also    | fi xp2hex<br>toSFi xp<br>toUFi xp                                                                                                                                                                                                                                                                                                                                                                                                                            | Convert a signed value to a hex string represented by fxd-bits.<br>Converts a signed fractional value to fit in SFxd bits.<br>Converts an unsigned fractional value to fit in UFxd bits. |

#### listSched

| Purpose     | Find the SSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | using a List Scheduling method.                                                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | tFrames = li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | stSched(adj Mat, del ayVec, mul Ops, nMULs, nALUs)                                                                                                                                      |

| Description | tFrames = listSched(adj Mat, del ayVec, mul Ops, nMULs, nALUs) returns a two-<br>column vector 'tFrames' describing the SSG (Scheduled Sequencing Graph) of<br>the operations when scheduled according to a specified List Scheduling method<br>under resource constraints. The unscheduled flow has to be given in adj Mat<br>with the latency per resource type (e.g. MUL, ALU) as integer number of clock<br>cycles specified in del ayVec.<br>In the vector mul Ops the resource type of the operations should be given (a 1<br>means a multiplication), and the available numbers of resources in nMULs and<br>nALUs. |                                                                                                                                                                                         |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |

| See Also    | ALAP<br>ASAP<br>IistSched<br>parse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Find the SSG using the ALAP method.<br>Find the SSG using the ASAP method.<br>Find the SSG using the List Schedu;ing method.<br>Read and convert a .cir-file into internal data format. |

toAdj Mat Converts an interconnection table into an adjacency matrix.

### MUL

| Purpose     | Simulate the behavior of the VHDL description of a registered MULtiplier.                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | result = MUL(op1, op2, fxd)                                                                                                                                                                                                                                                                                                        |

| Description | result = MUL( $op1$ , $op2$ , fxd) returns the (signed) result of the multiplication of op1 and op2 (both signed).<br>The binary fixed-point format of result, as well as that of op1 and op2 should be given in the vector fxd as [N M], where N denotes the total number of bits, while M defines the number of fractional bits. |

| Examples    |                                                                                                                                                                                                                                                                                                                                    |

| See Also    | ALU simulate the behavior of the VHDL description of a registered ALU.                                                                                                                                                                                                                                                             |

#### parse

| Purpose     | Read and convert a .cir-file into internal data format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax      | CIRC_Data = parse(inFilename)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Description | CIRC_Data = parse(inFilename) extracts data from a textual circuit<br>description in a .cir-file. The data returned in the structure CIRC_Data contains<br>the following fields.<br>CIRC_Data. i ocDef<br>CIRC_Data. i connTbl<br>CIRC_Data. xconnTbl<br>CIRC_Data. opTypes<br>CIRC_Data. opTypes<br>CIRC_Data. opNames<br>CIRC_Data. i npNames<br>CIRC_Data. outNames<br>CIRC_Data. dl ydl nps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | CIRC_Data. i ocDef is a string defining the characters that are used as the first character in an opName to identify inputs, outputs and constant coefficients with. CIRC_Data. i connTbl is a (number of operations x 4) array that describes the interconnections between the operations. The first column list the operation identification numbers (opi d#), where the corresponding type and name of an opi d# can be found in CIRC_Data. opTypes and CIRC_Data. opNames respectively. Columns 2 and 3 list the opi d#s of the operations that are connected to this opi d#'s inputs. A negative sign is used to indicate that the input is connected to an input port (i np#), the name of which can be found as entry i np# in the cell-vector CIRC_Data. i npNames. Output ports (outp#) are given in column 4, while their names are listed in CIRC_Data. outNames. If no shift operations (<< or >>) are present, i connTbl is a one dimensional (number_of_operations,4) array, else a (number_of_operations,4,2) array. |

|             | opTypes: mul, add, sub,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | CIRC_Data.xconnTbl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | CIRC_Data.dlydlnps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Examples    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| See Also    | Groupl Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## read\_OUT

| Purpose          | Convert the hex data in an .OUT-file into decimal format.                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax           | y = READ_OUT(outFilename, fxd2)<br>y = READ_OUT(outFilename, fxd2, nOutputs)<br>y = READ_OUT(outFilename, fxd2, nOutputs, nFracDigits)                                                                                                                                                                                                                                                            |

| Description      | $y = READ_OUT(outFilename, fxd2)$ returns the hex data as read from<br>outFilename in a decimal format specified by the vector fxd2 ([N M] fixed-point<br>format). Output is also displayed in the console window.                                                                                                                                                                                |

|                  | y = READ_OUT(outFilename, fxd2, nOutputs) should be used if the circuit for which outFilename is valid, shows more then one outputs. y will become a column vector with as many rows as given by nOutputs.                                                                                                                                                                                        |

|                  | $y = READ_OUT(outFilename, fxd2, nOutputs, nFracDigits) can be used to limitthe number of fractional digits that are displayed in the console window (defaultthe sum of the numbers of digits for the whole part, the fractional point and forthe fractional part together is 17).$                                                                                                               |

| Examples         | <pre>&gt;&gt; o5 = read_OUT('FIR5\vhdl\FIR5.OUT',[17 15],1,5);<br/>1: x"00000" = 0.00000<br/>2: x"00000" = 0.00000<br/>4: x"1F654" = -0.07556<br/>5: x"00203" = 0.01572<br/>6: x"03F11" = 0.49271<br/>7: x"07C1F" = 0.96970<br/>8: x"087CE" = 1.06097<br/>9: x"07E22" = 0.98541<br/>10: x"07E22" = 0.98541<br/>11: x"07E22" = 0.98541<br/>12: x"07E22" = 0.98541<br/>13: x"07E22" = 0.98541</pre> |